数字IC设计后端流程的7个环节详解 - 从逻辑综合到生成版图

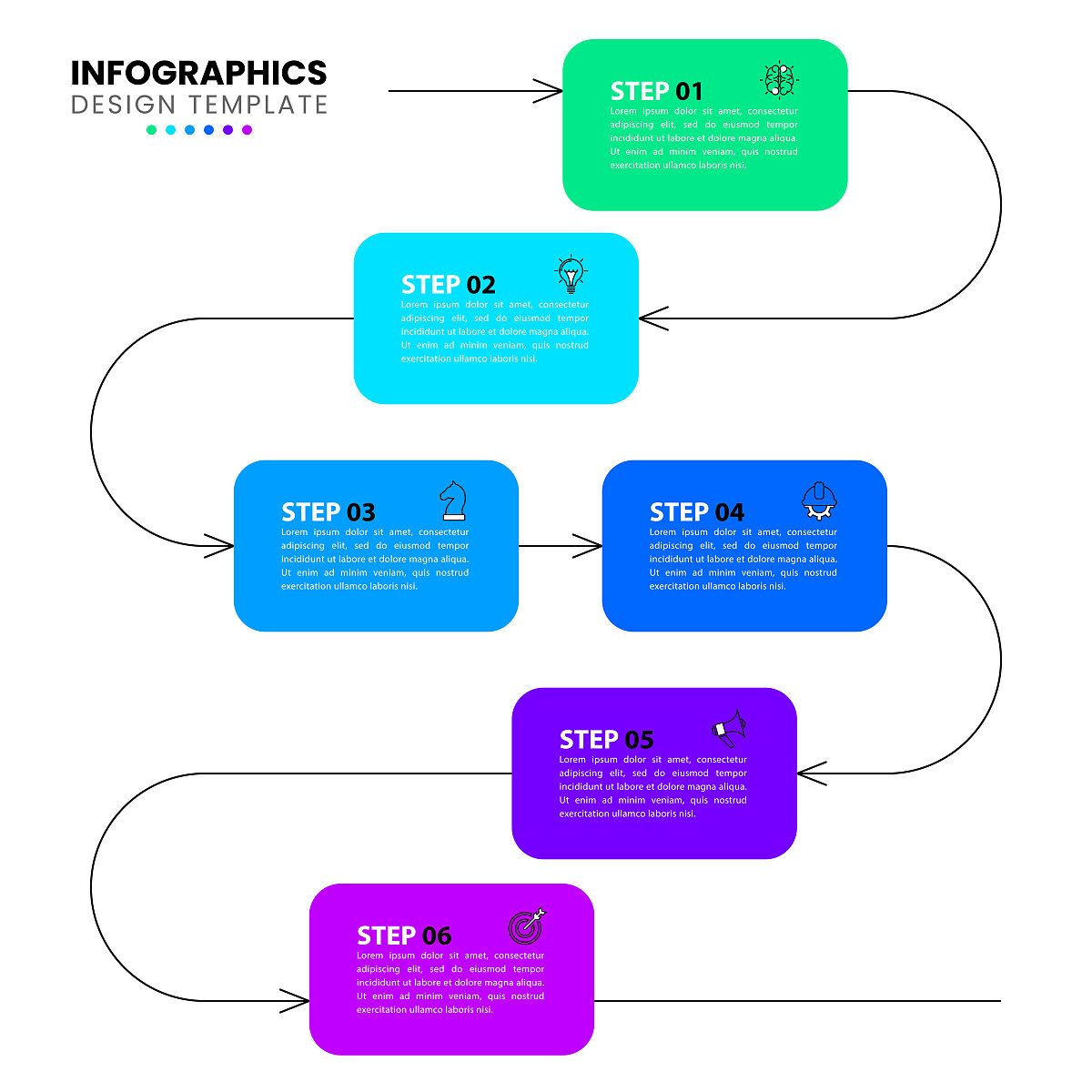

数字IC设计的后端流程是指将经过前端设计验证的电路描述文件转换为可制造的芯片的过程。该流程主要包括7个环节:逻辑综合、门级综合、布局布线、时序优化、时序验证、物理验证和生成版图。

-

逻辑综合:将电路描述文件(如Verilog或VHDL)转换为门级网表,即使用基本逻辑门来实现电路功能。

-

门级综合:对逻辑综合生成的网表进行优化,例如移除冗余逻辑,并根据目标工艺库进行映射,以生成更紧凑、更高效的电路。

-

布局布线:将优化后的网表中的逻辑门和互连线放置在芯片上,并连接各个逻辑门之间的信号。

-

时序优化:根据时序约束,对布局布线的结果进行优化,以满足设计的时序要求。

-

时序验证:对时序优化后的结果进行验证,确保设计能够满足时序要求。

-

物理验证:对布局布线后的结果进行物理验证,确保设计符合工艺规则,并能够顺利制造。

-

生成版图:根据物理验证的结果,生成芯片的版图文件,并将其发送给晶圆厂进行生产。

原文地址: https://www.cveoy.top/t/topic/pJRw 著作权归作者所有。请勿转载和采集!