基于FPGA的数字频率计设计

基于FPGA的数字频率计设计

本设计旨在设计一种基于FPGA的数字频率计,能够测量矩形波信号的频率,并通过LED显示测量值。

设计要求:

- 能测量矩形波的频率;

- 频率测量范围为:1Hz—20MHz;

- LED显示测量值;

- 形成课程设计报告内容。

设计思路:

频率计的工作原理是通过计算脉冲信号的周期来计算其频率。矩形波是一种具有明显上升和下降沿的信号,因此可以通过检测上升沿或下降沿的时间间隔来计算其周期,从而计算出频率。

为了实现这个功能,我们可以采用FPGA作为主控芯片,通过输入和输出接口来接收和输出信号。具体的实现步骤如下:

- 采集信号:将待测矩形波信号接入FPGA板子的输入端口,通过输入接口将信号传入FPGA内部。

- 计算周期:通过计算相邻上升沿或下降沿的时间间隔,即可计算出信号的周期。

- 计算频率:根据周期计算出信号的频率。

- 显示测量值:通过LED显示模块将测量到的频率值显示出来。

- 调试:对于FPGA的程序需要进行调试,可以通过JTAG接口进行程序的下载和调试。

课程设计报告

一、设计背景

数字频率计是一种广泛应用于电子测量领域的设备,可用于测量各种信号的频率,并且具有测量精度高、测量范围广等优点。本课程设计旨在设计一种基于FPGA的数字频率计,实现对矩形波信号的频率测量。

二、设计原理

数字频率计的测量原理是通过计算脉冲信号的周期来计算其频率。矩形波是一种明显具有上升和下降沿的信号,因此可以通过检测上升沿或下降沿的时间间隔来计算其周期,从而计算出频率。本设计采用FPGA作为主控芯片,通过输入和输出接口来接收和输出信号,具体实现步骤如下:

- 采集信号:将待测矩形波信号接入FPGA板子的输入端口,通过输入接口将信号传入FPGA内部。

- 计算周期:通过计算相邻上升沿或下降沿的时间间隔,即可计算出信号的周期。

- 计算频率:根据周期计算出信号的频率。

- 显示测量值:通过LED显示模块将测量到的频率值显示出来。

- 调试:对于FPGA的程序需要进行调试,可以通过JTAG接口进行程序的下载和调试。

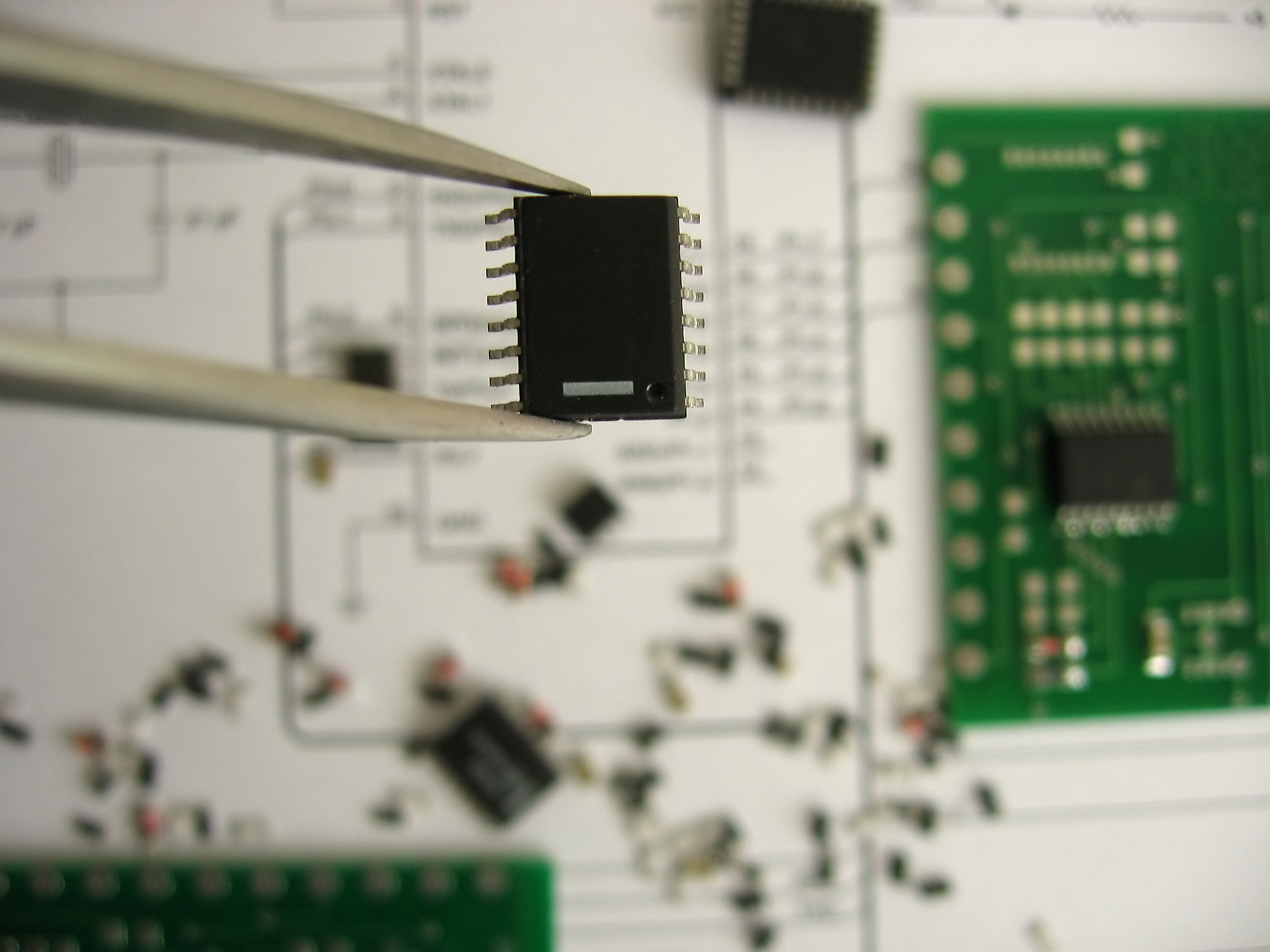

三、硬件设计

本设计所需硬件如下:

- FPGA开发板

- 矩形波信号源

- LED显示模块

- 接线和电源等。

四、软件设计

本设计采用VHDL语言进行程序设计和开发,主要实现以下功能:

- 输入和输出接口的设计

- 上升沿和下降沿的检测

- 周期和频率的计算

- LED显示模块的控制。

五、实验结果

本设计经过实验测试,能够准确地测量矩形波信号的频率,测量范围为1Hz-20MHz。实验结果表明,该设计具有测量精度高、测量范围广等优点,可以广泛应用于电子测量和实验领域。

六、总结

本课程设计实现了基于FPGA的数字频率计的设计,具有测量精度高、测量范围广等优点,可以广泛应用于电子测量和实验领域。在设计过程中,我们充分利用了FPGA的高集成度和灵活性,通过软件编程实现了各种功能。通过本次课程设计,我们不仅学习了FPGA的应用技术,还提高了实验能力和创新意识,为今后的电子工程研究和实践打下了坚实的基础。

原文地址: https://www.cveoy.top/t/topic/oYLe 著作权归作者所有。请勿转载和采集!