FPGA实现3-8译码器设计:电路原理图、程序调试及实验结果

FPGA实现3-8译码器设计:电路原理图、程序调试及实验结果

本项目使用FPGA实现3-8译码器,详细介绍了电路原理图、程序调试过程以及实验结果。

设计要求:

- 采用图形输入法设计三八译码器,并进行编译、仿真。

- 将程序下载至FPGA开发板,用四位拨码开关代表译码器的输入端a、b、c、en,将之分别与芯片的相应管脚相连。

- 用LED灯来表示译码器的输出,将y7…y0对应的管脚分别与8只LED灯相连,观察实验结果。

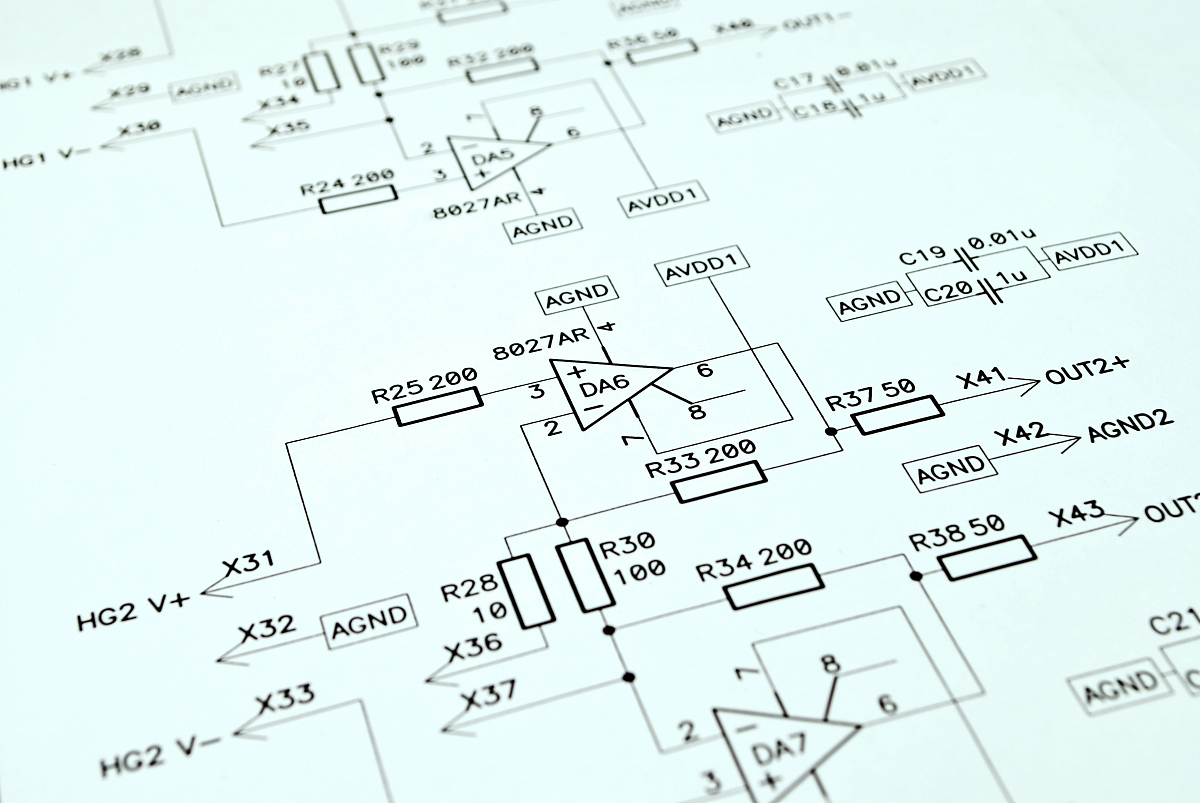

电路原理图如下:

程序调试图片如下:

原文地址: https://www.cveoy.top/t/topic/oDuf 著作权归作者所有。请勿转载和采集!