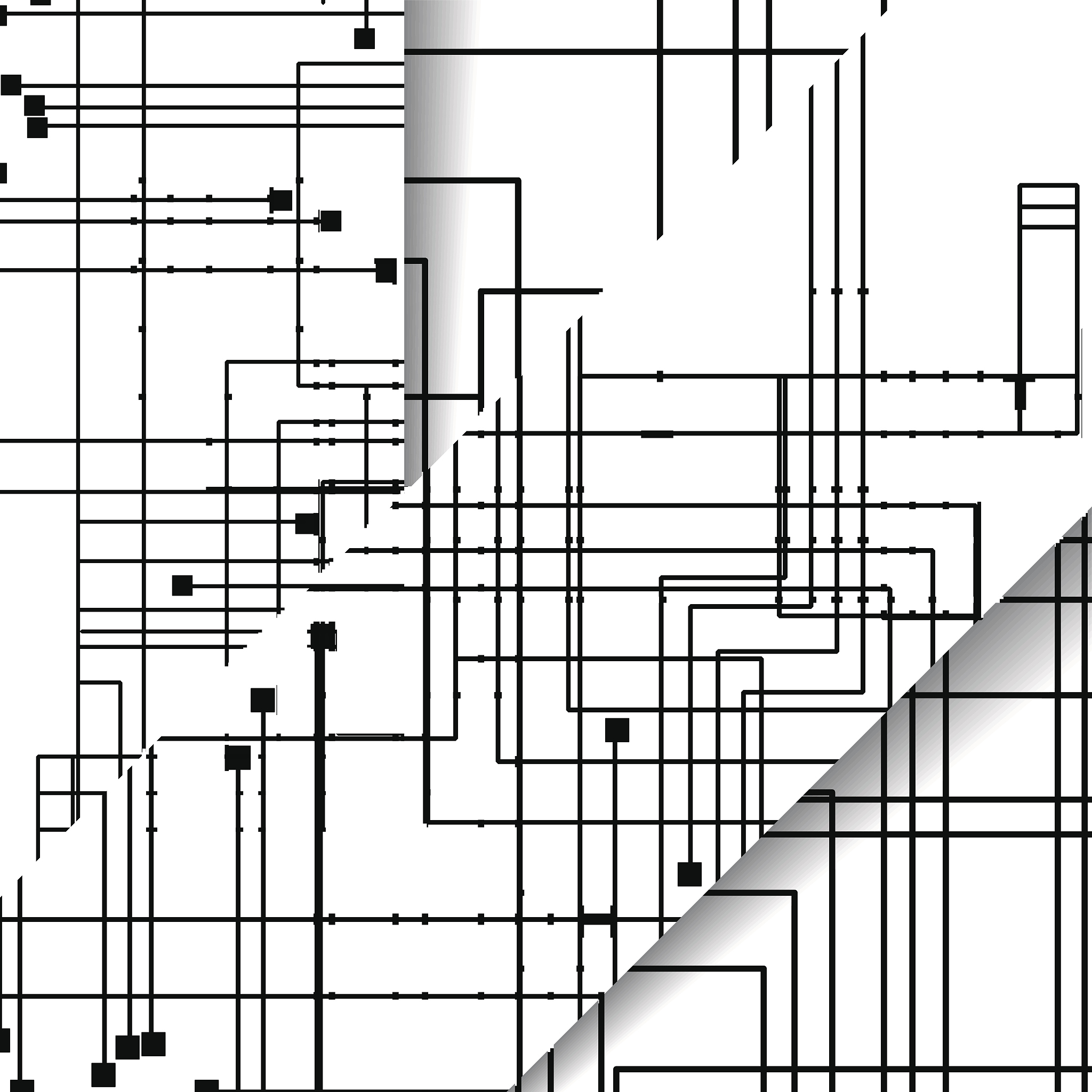

四位余三码到8421码转码电路设计与逻辑电路图

以下是一个设计四位余三码到8421码的转码电路的示例逻辑电路图:

______

D0 ---| |

| 8421|--- Y0

D1 ---| 余3 |--- Y1

|码转码|

D2 ---| |--- Y2

|______|

D3 ---| |

| 8421|--- Y3

GND ---| 余3 |

|码转码|

VCC ---|______|

在上述电路图中,D0、D1、D2、D3 表示输入的四位余三码,Y0、Y1、Y2、Y3 表示输出的8421码。

该电路采用了一组四个编码器,在输入的四位余三码上进行编码转换。每个编码器都有六个输入引脚和四个输出引脚。输入引脚 D0、D1、D2、D3 分别连接到四位余三码的输入线上。输出引脚 Y0、Y1、Y2、Y3 分别连接到8421码的输出线上。

根据编码器的真值表,根据输入引脚的状态,编码器会将其转换为相应的8421码输出。根据四位余三码的不同组合,通过编码器将其转换为相应的8421码,实现了转码的功能。

请注意,在实际应用中,可能需要添加适当的电平转换电路、输入缓冲器和输出缓冲器,以确保电路的正常工作和防止电路的损坏。

原文地址: https://www.cveoy.top/t/topic/mvP 著作权归作者所有。请勿转载和采集!