使用逻辑分析仪调试RS232串口通信:Verilog UART发送示例

使用逻辑分析仪调试RS232串口通信:Verilog UART发送示例

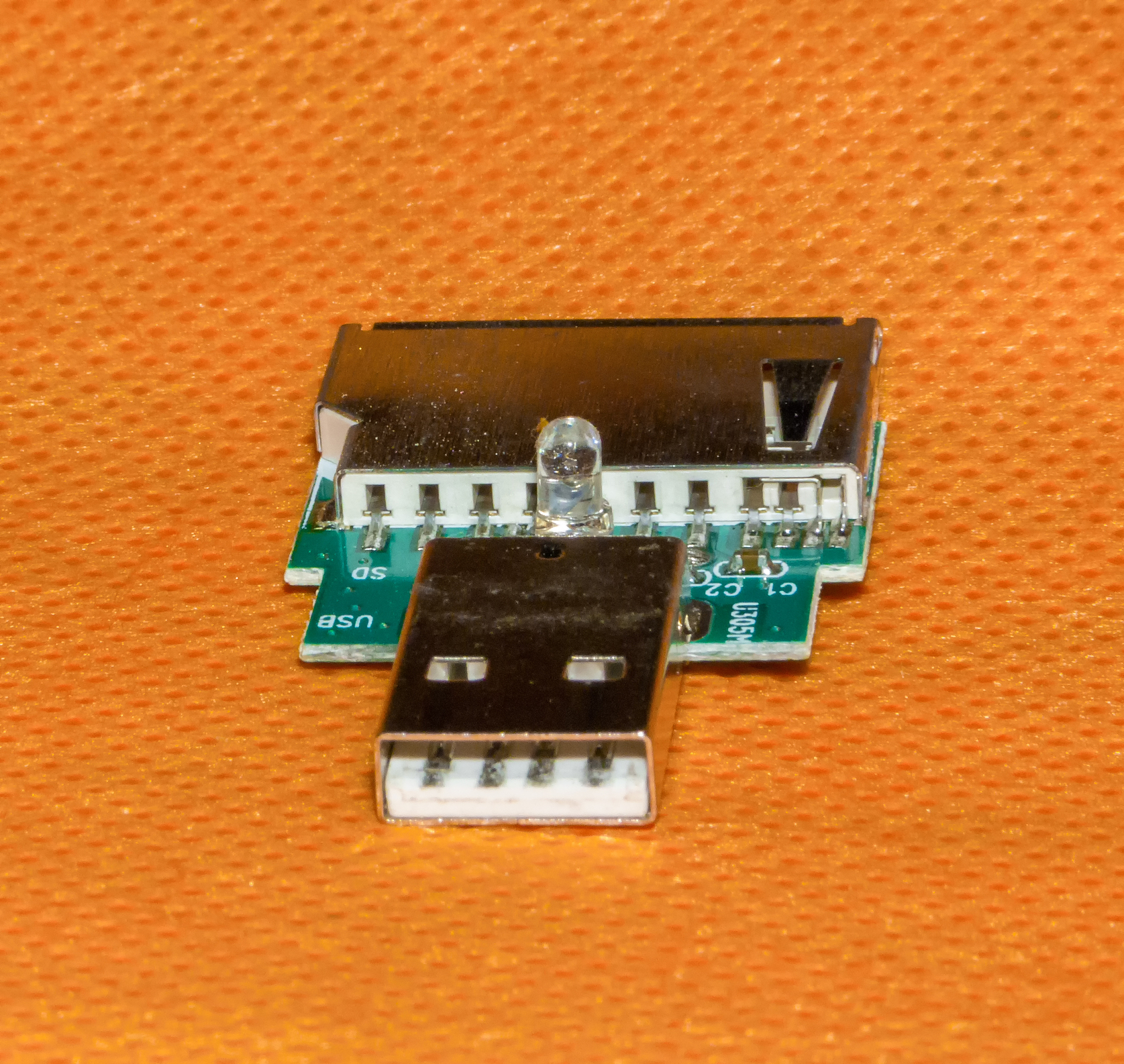

将逻辑分析仪的引脚连接到RS232芯片的TX和RX引脚后,可以使用Verilog在终端程序中发送字符内容。

首先,需要在Verilog中定义一个模块,该模块用于从终端程序发送字符到RS232芯片。下面是一个示例模块:

module uart_tx(

input clk, // 时钟信号

input reset, // 复位信号

input [7:0] data, // 要发送的数据

output tx // RS232芯片的TX引脚

);

reg [3:0] state; // 状态寄存器

reg [7:0] shift_reg; // 移位寄存器

reg start_bit; // 起始位

reg stop_bit; // 停止位

assign tx = stop_bit ? 1'b1 : shift_reg[0]; // 输出TX信号

always @(posedge clk) begin

if (reset) begin

state <= 4'b0000;

shift_reg <= 8'b00000000;

start_bit <= 1'b0;

stop_bit <= 1'b1;

end else begin

case (state)

4'b0000: begin // 等待发送

shift_reg <= data;

start_bit <= 1'b0;

stop_bit <= 1'b0;

state <= 4'b0001;

end

4'b0001: begin // 发送起始位

start_bit <= 1'b1;

state <= 4'b0010;

end

4'b0010: begin // 发送数据位

shift_reg <= {1'b0, shift_reg[7:1]};

state <= 4'b0011;

end

4'b0011: begin // 发送停止位

stop_bit <= 1'b0;

state <= 4'b0000;

end

endcase

end

end

endmodule

在终端程序中,可以使用串口通信库(如PySerial)来打开串口,并发送字符到该模块。下面是一个示例Python代码:

import serial

ser = serial.Serial('/dev/ttyUSB0', 9600) # 打开串口

ser.write(b'Hello, world!

') # 发送字符串

ser.close() # 关闭串口

这将向RS232芯片的TX引脚发送字符'Hello, world!'(带有回车和换行)。逻辑分析仪可以用来检查实际发送的数据是否与预期相符。

通过逻辑分析仪的波形,你可以观察到发送的数据信号,包括起始位、数据位和停止位,并确保它们符合RS232协议规范。这将帮助你调试串口通信过程中的问题,例如数据错误、时序问题等等。

原文地址: https://www.cveoy.top/t/topic/m0lv 著作权归作者所有。请勿转载和采集!