用PLL消除相位噪声具体应该怎么做

PLL(Phase Locked Loop)是一种常用的消除相位噪声的技术。下面是一些具体的步骤:

-

确定参考信号:PLL需要一个稳定的参考信号来比较和锁定输出信号的相位。参考信号可以是外部信号,如晶振或GPS信号,也可以是内部信号,如PLL内部产生的信号。

-

比较相位差:将参考信号和输出信号输入相位比较器,比较器会输出一个表示相位差的信号。

-

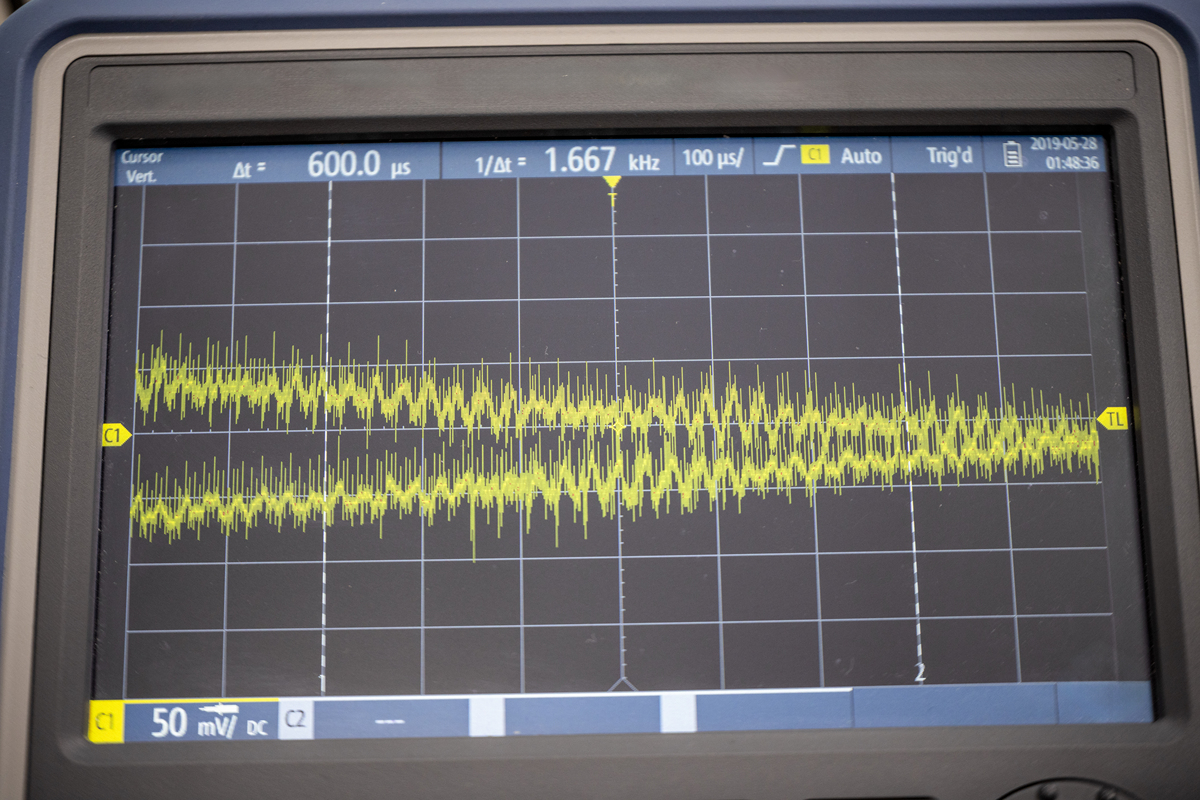

产生控制电压:将相位差信号输入低通滤波器,滤波器会产生一个平滑的控制电压,用于调节VCO(Voltage Controlled Oscillator)的频率。

-

调节VCO频率:将控制电压输入VCO,VCO会根据控制电压的大小调节自己的频率,使输出信号的相位与参考信号的相位保持一致。

通过以上步骤,PLL可以消除输出信号中的相位噪声,并使其与参考信号保持同步。需要注意的是,PLL的设计和调试需要一定的专业知识和经验,否则可能会出现锁定失败或者震荡等问题。

原文地址: https://www.cveoy.top/t/topic/fpdU 著作权归作者所有。请勿转载和采集!