数字集成电路低功耗设计的难点

数字集成电路低功耗设计的难点包括以下几个方面:

-

电源噪声和供电稳定性问题:低功耗设计需要使用低电压、低功耗的器件,但这些器件对电源噪声和供电稳定性要求较高,因此需要采取一系列措施来降低电源噪声和提高供电稳定性。

-

时钟和时序问题:低功耗设计需要使用低频时钟和高效时序,但这会导致时钟和时序的稳定性和精度下降,因此需要采取一些优化措施来提高时钟和时序的稳定性和精度。

-

线性度和精度问题:低功耗设计需要使用低功耗、低噪声、高精度的模拟电路和数字电路,但这些电路的线性度和精度往往较低,需要采取一些优化措施来提高电路的线性度和精度。

-

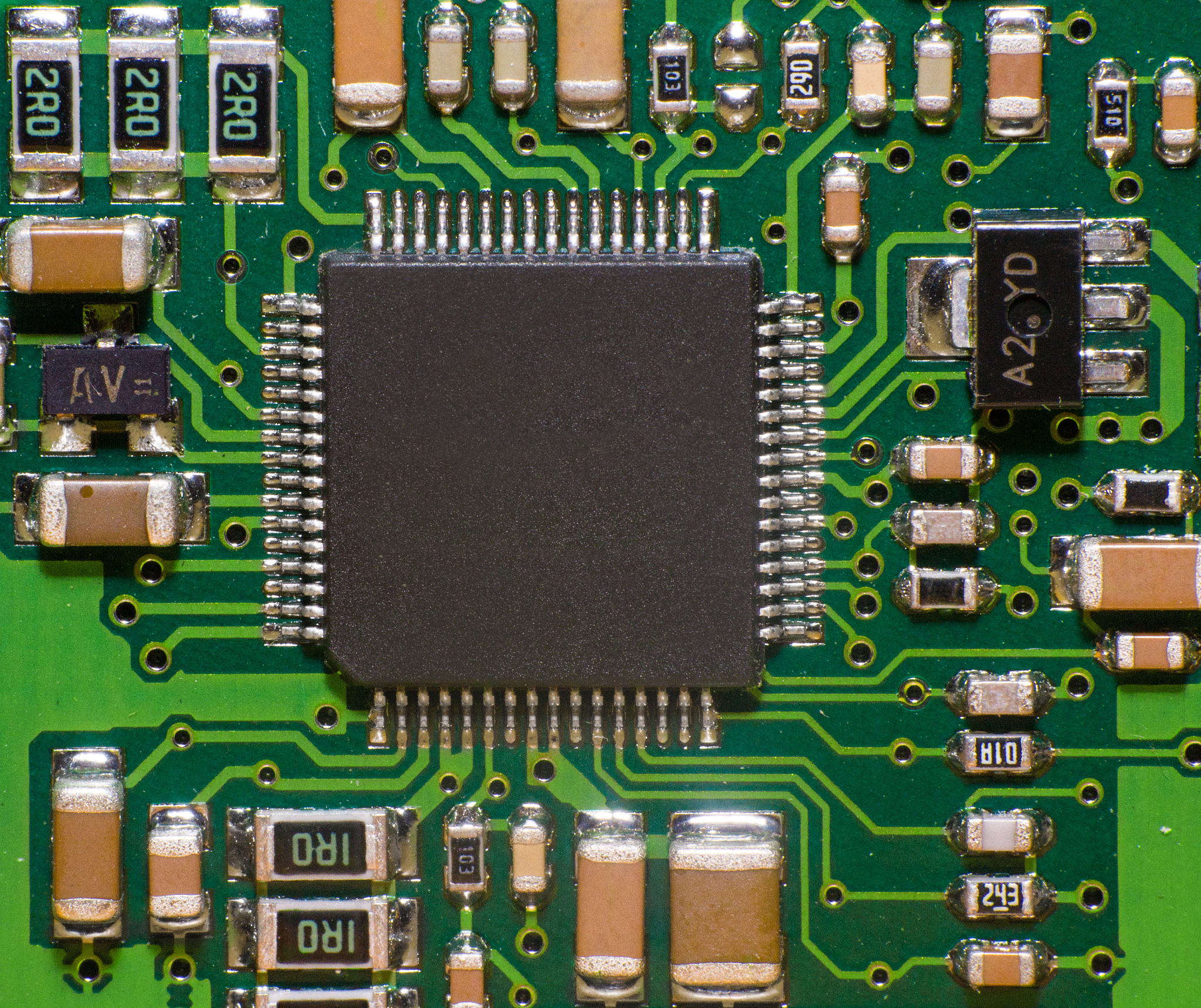

芯片布局和封装问题:低功耗设计需要在芯片布局和封装上采取一些优化措施,以提高芯片的散热性能和抗干扰能力,同时还要保证芯片的可靠性和易制造性。

-

系统级优化问题:低功耗设计需要在系统级上采取一些优化措施,如采用功耗管理技术、优化算法等,以提高系统的功耗效率和性能表现。

原文地址: https://www.cveoy.top/t/topic/fjTL 著作权归作者所有。请勿转载和采集!