改写合并以下内容从世界上第一块集成电路问世1958 年以来半导体制造工艺不断发展、设计方法不断改进使得电路集成规模迅速增大产品性能越来越高使用起来也越来越方便。尤其是在上世纪七十年代以后集成电路行业发展更加迅速处理器中的晶体管数目从最早的几千个增长到了现在的几十亿个随时间呈现指数型的增长。超大规模集成电路的发展有两个主要的方向即高性能和高可靠性。从一个方面来说集成电路朝着集成度更高的方向发展更多的

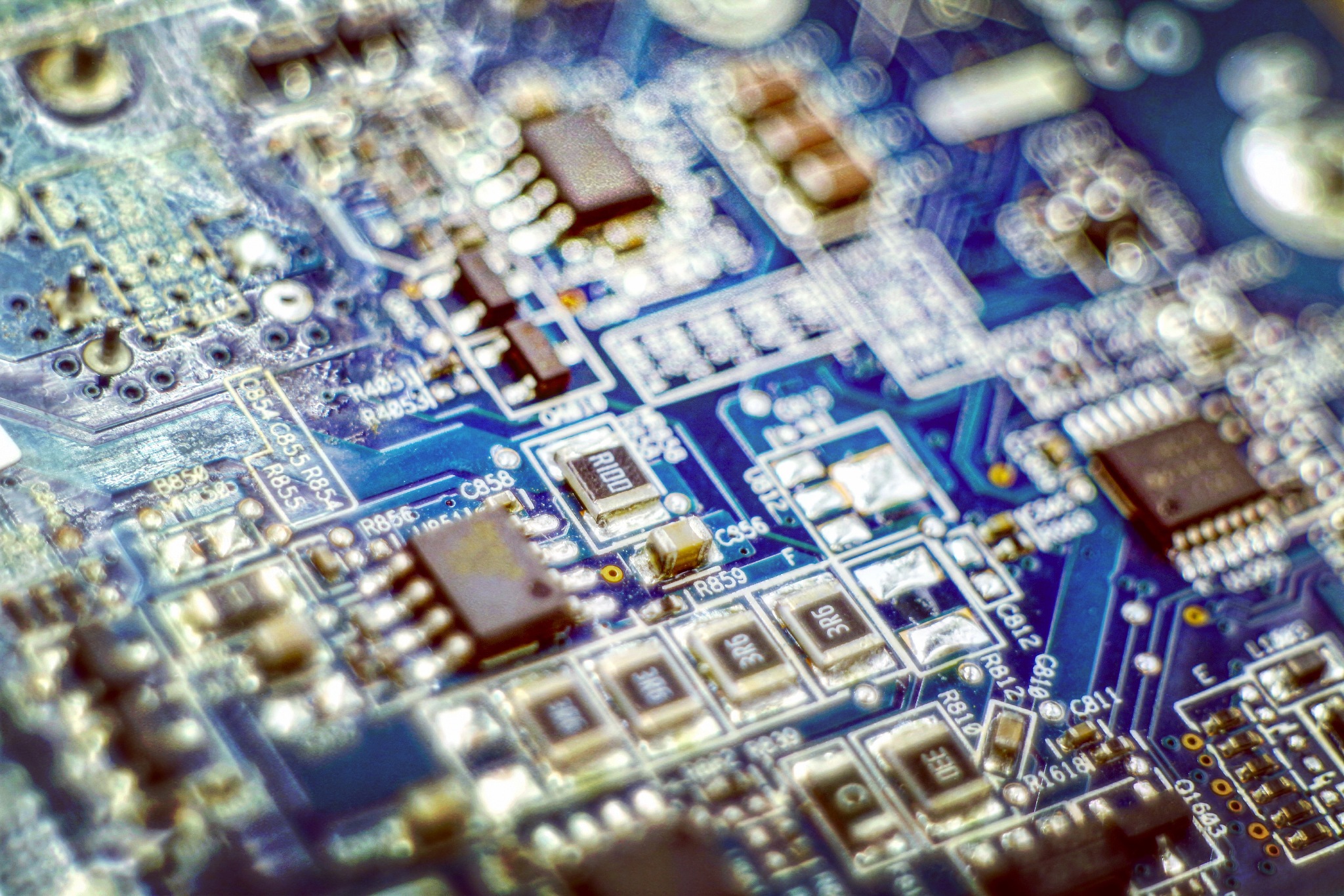

自1958年世界上第一块集成电路问世以来,半导体制造工艺和设计方法一直在不断发展改进,使得电路集成规模迅速增大,产品性能越来越高,使用起来也越来越方便。尤其是在上世纪七十年代以后,集成电路行业发展更加迅速,处理器中的晶体管数目从最早的几千个,增长到了现在的几十亿个,随时间呈现指数型的增长。集成电路的发展方向主要有两个,即高性能和高可靠性。集成电路朝着集成度更高的方向发展,更多的晶体管集成在芯片上,可以实现更多的功能,同时可靠性也成为超大规模集成电路发展中要考虑的重要问题。随着近年来太空探索等航空航天事业的快速发展,航空电子设备的抗辐射性能需要进一步提高,辐射可靠性也成为航空航天电子设备要考虑的重要问题之一。

从二十年代末开始,IC技术的发展更加迅速,使其在性能和集成度等方面不断超越以前的产品。为了降低研究和制造成本并提高性能,研究者们试着引入新材料、新工艺和新器件结构,这为集成电路的可靠性带来了一系列问题。随着特征尺寸的不断减小,一些材料已经接近其物理极限,使得对其测试和寿命评估更加困难。材料和工艺的更新也带来了新的可靠性问题。例如,金属互连制造工艺中引入的低K和超低K介质,其电学热学和机械性能远远低于二氧化硅材料,加上击穿电压、栅氧化层经时击穿(TDDB)时间和高密度封装引起的新的失效机理,已经成为了集成电路可靠性的一个严重的制约因素。尺寸缩小与集成度提高使可靠性测试更加有难度。因为尺寸缩小使器件对静电放电(ESD)更加敏感,集成度的提高也使电路的可靠性评估变得更为复杂。集成电路高速发展的同时,也为集成电路带来了巨大的可靠性问题,研究者们需要深入研究可靠性机理,并改进可靠性评估方法,降低集成电路尺寸缩小带来的限制,保证产品在工作中有足够的可靠性容限。

在1947年贝尔实验室制作出了世界上的第一个晶体管,随后在1940年Schockley发明出来了双极型晶体管,之后Harris在1956年用分立的元件发明了采用双极型晶体管制作的第一个数字逻辑门,在1962年出现了世界上的第一款真正成功的IC逻辑系列TTL(晶体管-晶体管逻辑)。然而,由于双极晶体管本身的原因导致用其制作的数字逻辑每个门的功耗太大,最终限制了可以可靠的集成在单片、封装和机壳或机箱上的逻辑门的最大数目,最终使MOS数字集成电路发展起来并且占据了支配的地位。在CMOS技术的推动下,集成电路的密度与性能随着单片上集成的晶体管数量的增加而增加,目前市场上的处理器中晶体管数目已经达到十亿以上,台积电的10nm制程的工艺已经投产,而intel已经在研发最新的7nm制程的工艺。

由于集成电路的复杂度和集成的晶体管数量的不断增加,以及日益缩小的器件特征尺寸,一旦集成电路上的某一个器件出现问题而无法工作,便会导致其他器件的负荷增加,降低该器件的寿命最终加速整个电路的失效。因此集成电路以及器件的可靠性越来越受到重视,器件的可靠性是指在器件的额定工作条件下,该器件能够实现它预先设计好的功能工作所需要的时间的概率。器件在深亚微米尺寸下,由于其超薄的栅介质层的厚度,导致了很强的栅电场,严重的削弱了器件的可靠性。目前主要存在的可靠性问题有热载流子注入效应(HCI)、负栅压温度不稳定性(NBTI)和超薄栅氧化层经时击穿效应(TDDB)。在NBTI应力的作用之

原文地址: https://www.cveoy.top/t/topic/esWt 著作权归作者所有。请勿转载和采集!