全加器、半加器的实验总结

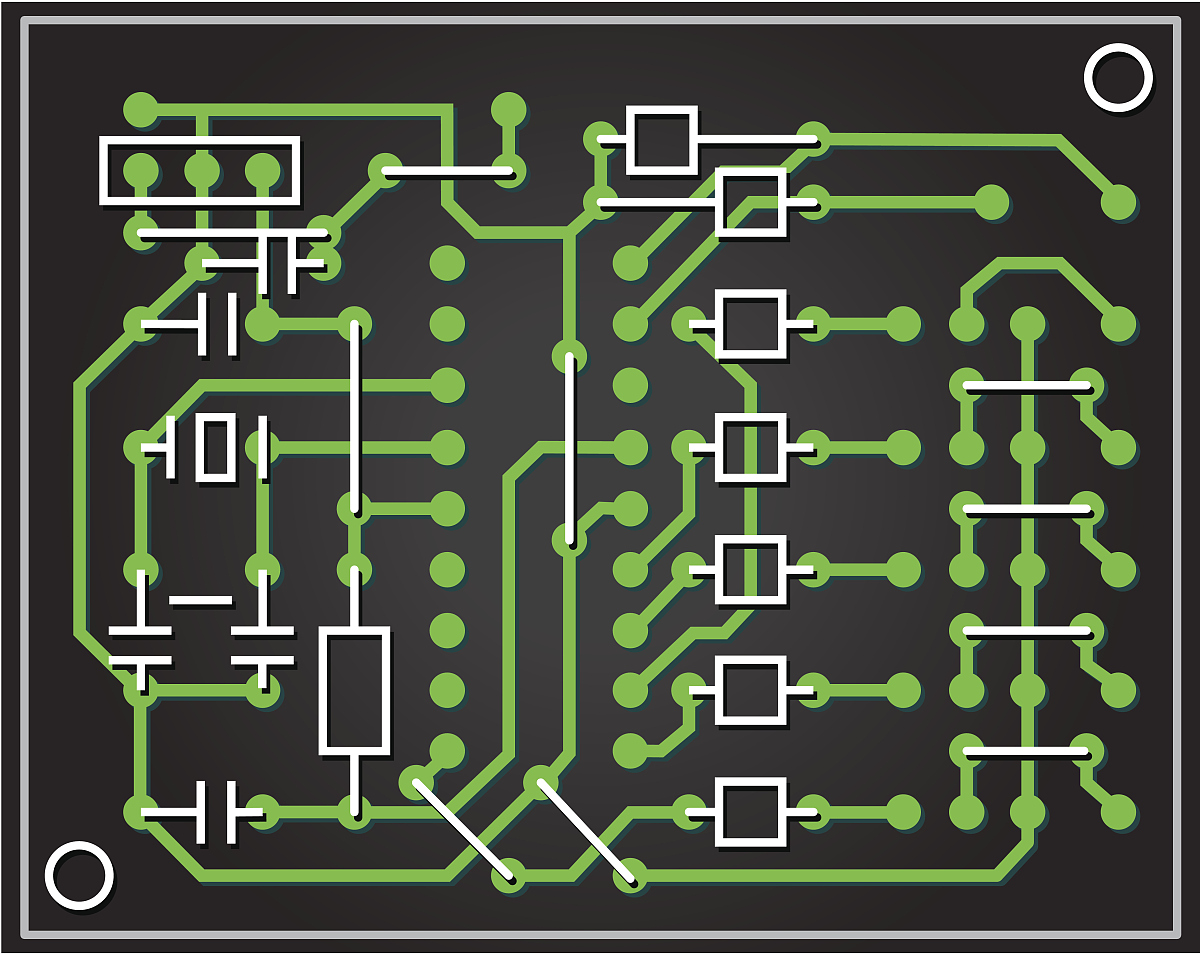

全加器和半加器是数字电路中常用的基本电路,用于实现加法运算。在实验中,我们通过使用逻辑门和电子元件来构建全加器和半加器电路,并测试其功能和性能。

实验中我们使用了以下材料和工具:

- 逻辑门:与门、或门、非门、异或门、与非门等。

- 电路板、电源、导线等电子元件。

- 逻辑分析仪、示波器等测试工具。

在实验中,我们首先学习了半加器和全加器的原理和实现方法。半加器是一个简单的电路,只能进行两个一位二进制数的加法运算,但是不能处理进位。全加器可以处理进位,可以进行三个一位二进制数的加法运算。因此,全加器比半加器更加实用。

我们使用逻辑门和电子元件来构建半加器和全加器电路,并进行测试。在测试中,我们输入不同的二进制数,观察输出结果是否正确。如果输出结果与预期结果不一致,则需要检查电路布局和元件连接,查找错误并进行修复。

在实验中,我们还学习了数字电路的设计方法和思路。数字电路的设计需要考虑电路的功能、性能、稳定性等因素,需要进行详细的设计和模拟,以确保电路的正确性和可靠性。我们使用CAD软件进行数字电路的设计和模拟,可以有效提高设计的效率和精度。

总的来说,通过实验,我们深入了解了数字电路中半加器和全加器的原理和实现方法,掌握了数字电路的设计方法和思路,提高了数字电路的设计和调试能力

原文地址: https://www.cveoy.top/t/topic/d8mq 著作权归作者所有。请勿转载和采集!