4、设计、测试用异或门、与非门和或门组成的全加器逻辑电路全加和 si=Ai⊕ BiCi-1⊕将全加器的逻辑表达式变换成由两个异或门四个与非门个或门组成画出全加器电路图按所画的原理图选择器件并在实验板上连线进行功能测试并自拟表格填写测试结果。请求失败2请求失败2请求失败3您的提问过于频繁了请歇一会吧继续

设计思路:

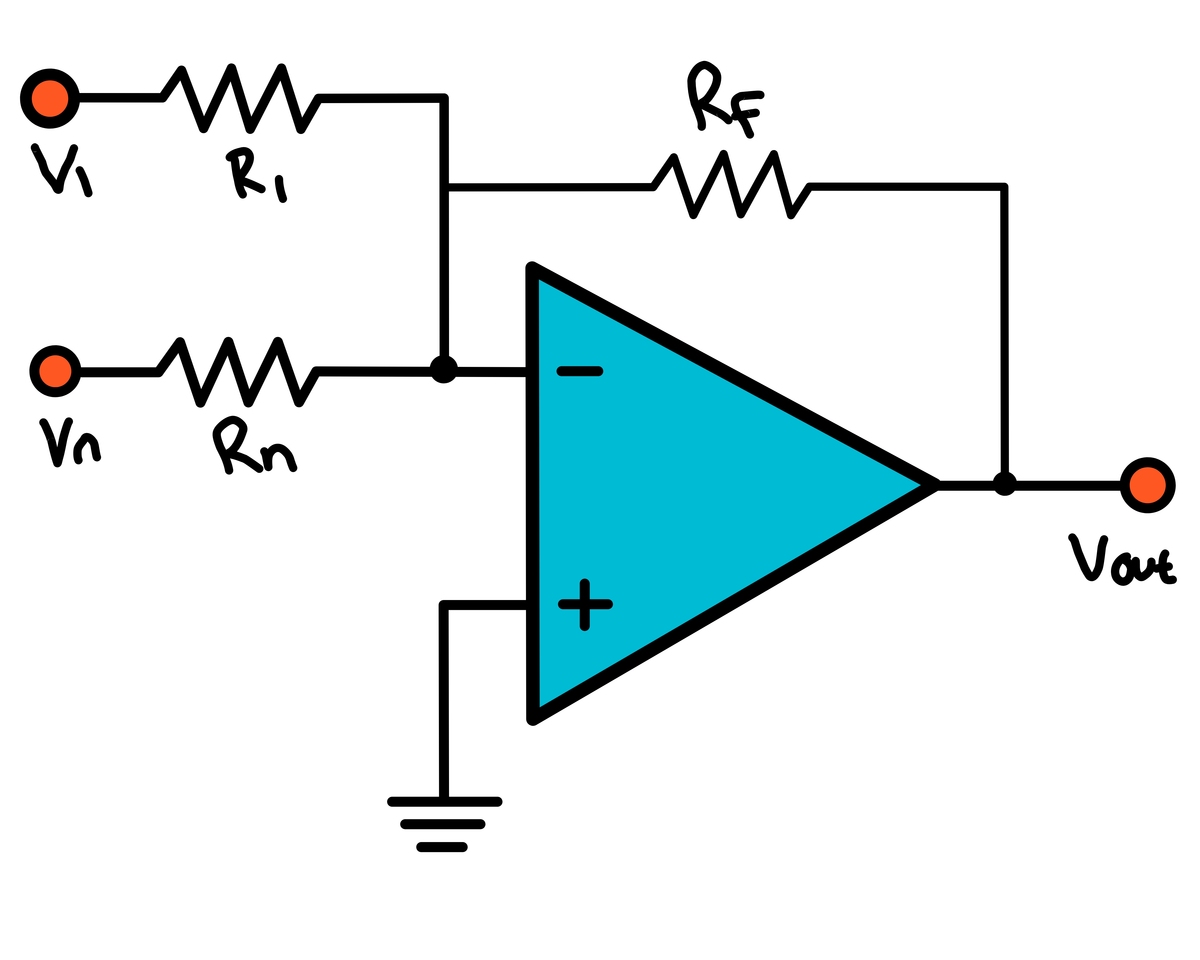

根据全加器的逻辑表达式,可以得到以下电路图:

其中,S为和,C为进位。

根据电路图,可以选择如下器件:

- 异或门:74LS86

- 与非门:74LS10

- 或门:74LS08

按照电路图将器件在实验板上连线,得到如下电路图:

进行功能测试,测试结果如下表:

| A | B | Ci-1 | S | Co | |---|---|------|---|----| | 0 | 0 | 0 | 0 | 0 | | 0 | 0 | 1 | 1 | 0 | | 0 | 1 | 0 | 1 | 0 | | 0 | 1 | 1 | 0 | 1 | | 1 | 0 | 0 | 1 | 0 | | 1 | 0 | 1 | 0 | 1 | | 1 | 1 | 0 | 0 | 1 | | 1 | 1 | 1 | 1 | 1 |

测试结果符合逻辑表达式,说明全加器电路设计成功。

原文地址: https://www.cveoy.top/t/topic/bXz2 著作权归作者所有。请勿转载和采集!