ICdesign-for-test设计压缩电路的原理

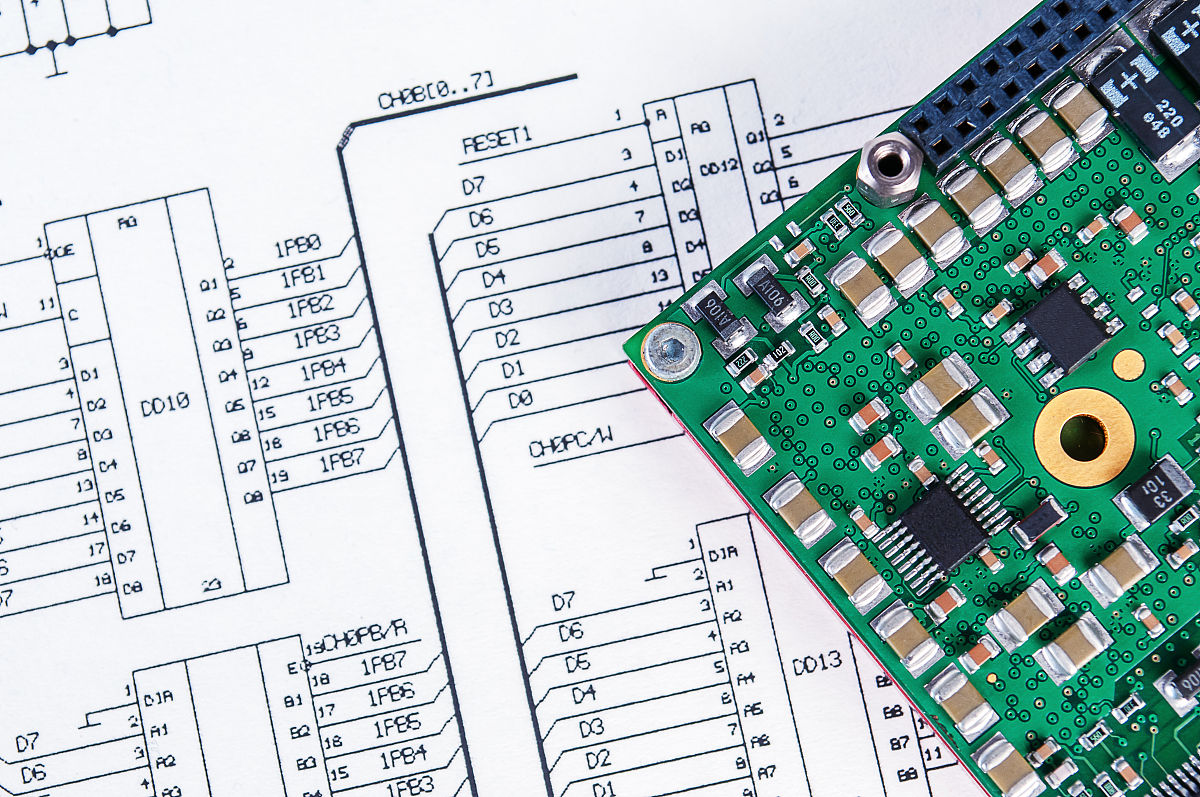

IC设计 for test是指在设计集成电路时,同时考虑测试的需求,以确保设计的可测试性。其中,压缩电路是测试中常用的一种技术。

压缩电路的原理是将测试数据压缩成更短的比特序列,以减少测试时间和测试数据的存储空间。常见的压缩电路包括编码器、解码器、移位寄存器等,它们通过对测试数据进行特殊编码和解码,将测试数据压缩成更小的比特序列。

例如,对于一个8位的测试数据,可以使用一个4位的编码器将其压缩成4位的比特序列。在测试时,将4位的压缩数据传输到芯片中,芯片内部的解码器将其还原成原始的8位测试数据。这样,测试时间和测试数据的存储空间就得到了显著的减少。

压缩电路的使用可以提高测试效率和可靠性,同时降低测试成本和测试时间。因此,在IC设计 for test中,压缩电路的设计和实现是非常重要的。

原文地址: http://www.cveoy.top/t/topic/fXq 著作权归作者所有。请勿转载和采集!